American Journal of Applied Sciences 5 (4): 312-319, 2008 ISSN 1546-9239 © 2008 Science Publications

# Low Power Modulo 2<sup>n</sup>+1 Adder Based on Carry Save Diminished-One Number System

Somayeh Timarchi, Omid Kavehei, and Keivan Navi Department of Electrical and Computer Engineering, Shahid Beheshti University, Tehran, Iran

**Abstract:** Modulo  $2^{n}+1$  adders find great applicability in several applications including RNS implementations. This paper presents a new number system called *Carry Save Diminished-one* for modulo  $2^{n}+1$  addition and a novel addition algorithm for its operands. In this paper, we also present a novel architectures for designing modulo  $2^{n}+1$  adders, based on parallel-prefix carry computation units. CMOS implementations reveal the superiority of the resulting adders against previously reported solutions in terms of implementation area and delay.

**Keywords:** Modulo  $2^{n}+1$  addition, carry save diminished-one number system, parallel-prefix adders, residue number system, computer arithmetic, VLSI circuits.

# **INTRODUCTION**

The Residue Number System (RNS) is a nonweighted number system <sup>[1]</sup> that can map large numbers to smaller residues, without any need for carry propagations <sup>[2]</sup>. Arithmetic operations like addition, subtraction and multiplication can be performed on residue digits concurrently and independently. Thus, using residue arithmetic, would in principle, increase the speed of computations <sup>[3,4,5]</sup>.

RNS has shown high efficiency in realizing special purpose applications such as digital filters <sup>[6, 7, 8, 9]</sup>, image processing <sup>[10]</sup>, RSA cryptography <sup>[11]</sup> and specific applications for which only additions, subtractions and multiplications are used and the number dynamic range is specific.

Special moduli sets have been used extensively to reduce the hardware complexity in the implementation of converters and arithmetic operations <sup>[12, 13]</sup>. Among which the triple moduli set  $\{2^n - 1, 2, 2^n + 1\}$  have some benefits <sup>[14]</sup>. Because of operand lengths of these moduli, the operation delay is determined by the modulo  $2^n$  +1 channel. Therefore, the design of efficient modulo  $2^n$  +1 adders is critical <sup>[15]</sup>. Modulo  $2^n$  +1 operations are used in many applications such as DSP algorithms <sup>[16]</sup>, Fermat Number Transform for elimination of round off errors in convolution computations<sup>[17, 18, 19]</sup>, cryptography<sup>[20]</sup> and in pseudorandom number generation<sup>[21]</sup>. Modulo  $2^n$  +1 adders are also utilized as the last stage adder of modulo  $2^n$  +1 multipliers.

In the last few years, several algorithms and architectures have been proposed for designing modulo  $2^{n}$ +1 adders. These algorithms are based on two number systems :

• To overcome the problem of (n+1)-bit wide circuits for the modulo  $2^n + 1$  channel, the diminished-one number system <sup>[17]</sup> has been proposed. In this system, efficient adders have been reported in <sup>[14, 22-25]</sup>. But these adders need a special treatment for zero operands.

For this problem, a new number representation called "Carry Save Diminished-one" (CSD-1) is proposed in this paper. With this system, the addition with zero operand doesn't need a special treatment, which reduces the adder chip area.

• Modulo 2<sup>n</sup> +1 adders can be designed as a special case of general modulo *m* adders. The most efficient circuits for generalized modulo adders are reported in <sup>[15, 26-28]</sup>. In <sup>[15]</sup>, the proposed adder is more efficient than the ones proposed by <sup>[26-28]</sup>.

However, the corresponding structure <sup>[15]</sup> uses a 3operand adder which is eliminated in our method. In the paper, we derive a new methodology for modulo  $2^n + 1$ adder that leads to a parallel-prefix adder architecture. Using implementation in a CMOS technology, we show that the proposed parallel-prefix design methodology uses considerably less chip area than that reported in <sup>[23]</sup> (diminished-one number system) and less chip area and propagation delay than the approach reported in <sup>[15]</sup> (normal number system).

#### FOUNDATION

**Modulo 2<sup>***n***</sup>** +1 **Reduction Basics :** Let A be a 2n bit word and  $A^h$  (resp.  $A^l$ ) the corresponding high (resp. low) *n* bit words:

**Corresponding Author:** Somayeh Timarchi, Faculty of Electrical and Computer Engineering, Shahid Beheshti University, Tehran, Iran, Tel: +98 21 29902286, Fax: +98 21 2417940, E-mail: s\_timarchi@sbu.ac.ir

$A = A^{h}2^{n} + A^{l}.$   $A \mod (2^{n} + 1) = (A^{h}2^{n} + A^{l}) \mod (2^{n} + 1)$  $= (A^{l} - A^{h}) \mod (2^{n} + 1).$

Therefore, the reduction modulo  $2^n + 1$  is computed by subtracting the high *n*-bit word from the low *n*-bit word and then conditionally adding  $2^n + 1$  if the subtraction yields a negative result.

**Diminished-One Number System:** In the diminishedone number system, the number A is represented by A' = A - 1 and the value zero is treated separately, i.e., it requires an additional zero indication bit. In this system, the ordinary addition can be implemented by an end-around-carry parallel-prefix adder with  $c_{in} = \overline{c_{out}}$

[17,25]:

$$S' = (S-1) = (A+B-1) \mod (2^{n}+1)$$

= [(A'+1) + (B'+1) - 1)] mod (2<sup>n</sup>+1)

= (A' + B' + 1) mod (2<sup>n</sup>+1)

= (A' + B' +  $\overline{c_{out}}$ ) mod 2<sup>n</sup> (1)

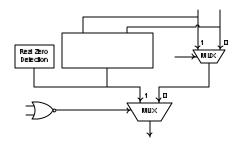

**Algorithm 1:** (Modulo  $2^n$  +1 addeition in diminished-1 number system): A number in diminished-one is represented by n+1 bits in which the  $(n+1)^{\text{th}}$  bit is used to indicate '0'. In <sup>[17]</sup>, the modulo  $2^n$  +1 addition algorithm has been presented for zero and non zero operands:

- 1) If the most significant bit of one addend is '1', inhibit the addition and the other addend is the sum (Fig. 1).

- If the msb of both addends are '0', ignore the msb, add the *n* lsb's, complement the carry and add it to the *n* lsb's of the sum.

The modulo  $2^n$  +1 adder in Fig. 1 can be designed in different ways. To increase the modulo addition speed, the delay of carry computation should be minimized. In many papers, parallel-prefix adders have been proposed for this purpose.

1 is extendable to any other modulo when diminishedone is only defined for modulo  $2^n + 1$ .

**CSD-1 Addition Algorithm:** In this section, we present the CSD-1 addition algorithm for modulo  $2^n$  +1 (Algorithm 2).

**Algorithm 2:** (CSD-1 addition): This algorithm is decomposed into 2 steps.

**Step 1.** The first step is based on the following theorem:

**Theorem 1:** Let A and B be two CSD-1 numbers in the range  $[0, 2^n+1]$ . Then,

$$|A+B|_{2^{n}+1} = \begin{cases} ||A+B-1|_{2^{n}} + 1|_{2^{n}} & \text{if } A+B-1 < 2^{n} \\ |A+B-1|_{2^{n}} & \text{otherwise} \end{cases}$$

**Proof:**

$$\begin{vmatrix} A+B \\ 2^{n}+1 \ = \begin{cases} A+B & \text{if } A+B < 2^{n}+1 \\ A+B-(2^{n}+1) & \text{otherwise} \end{cases}$$

(2)

$$= \begin{cases} (A+B-1)+1 & \text{if } A+B-1 < 2^{n} \\ (A+B-1)-2^{n} & \text{otherwise} \end{cases}$$

When  $A + B - 1 < 2^n$  then

$$(A+B-1)+1 = |A+B-1|_{2^n} + 1$$

(3)

The maximal value of (3) is  $2^n$ . In CSD-1, this value can be represented by (n+1) bits in *n* positions. In other words, the output carry resulting from  $|A+B-1|_{2^n}+1$  is 0. Thus, the term (3) is transformed into:

$$|A+B-1|_{2^n}+1=||A+B-1|_{2^n}+1|_{2^n}$$

Since  $A, B \in [0, 2^n]$ , the second case of equation (2) leads to the following inequalities:

$$A + B - 1 - 2^{n} \le 2^{n} + 2^{n} - 1 - 2^{n} < 2^{n}$$

So,

$$A + B - 1 - 2^{n} = |A + B - 1 - 2^{n}|_{2^{n}} = |A + B - 1|_{2^{n}}$$

Therefore, from (2) we get:

$$|A+B|_{2^{n}+1} = \begin{cases} |A+B-1|_{2^{n}} + 1 & \text{if } A+B-1 < 2^{n} \\ |A+B-1|_{2^{n}} & \text{otherwise} \end{cases}$$

(4)

The equation (4) outlines the impact of the output carry of (A+B-1). In the CSD-1 number system, this carry is produced when the sum is larger than  $2^n$ . The carry generation indicates that the sum is equal or greater than the modulo. Let assume  $C_{out}$  is the output carry of (A+B-1). Thus the carry of (A+B-1) will be generated when:

$$c_{out} = '1' \Leftrightarrow (A + B - 1) \ge 2^{n} + 1 \Leftrightarrow A + B \ge 2^{n} + 2$$

$$\Leftrightarrow A + B > 2^{n} + 1$$

(5)

Thus, if the sum of two numbers is greater than the modulo, the output carry of (A+B-1) is '1' and the sum is correct according to theorem 1: there is no need to increment the result.

The output carry is zero in the following cases:  $a_{n} = \frac{1}{2} \left( A + B - 1 \right) + 2^{n} + 1$

$$c_{out} = 0^{\circ} \Leftrightarrow (A + B - 1)^{\circ} < 2^{n} + 1$$

$$\Leftrightarrow A + B \le 2^{n} + 1 \quad \begin{cases} A + B < 2^{n} + 1 \quad (*) \\ A + B = 2^{n} + 1 \quad (**) \end{cases}$$

(6)

In condition (\*), since A+B is less than the modulo, the output carry of (A+B-1) is '0'. According to equation (4), the sum should be incremented in the second stage. Therefore from (4), (5) and (\*) we have: if  $A+B < 2^n + 1$  or  $A+B > 2^n + 1$  then:

$$S = (A+B) \mod (2^n+1) = (A+B-1) + \overline{c_{out}}$$

(7)

But in condition (\*\*) of equation (6), when  $A+B=2^n+1$ , equation (7) leads to S=1, which is not true. To correct this case, we introduce step 2 of Algorithm 2 that will be presented later.

In our method, (A+B-1) is computed without any extra hardware and only by ignoring  $a'_0$  in above sum. As mentioned earlier, if  $A \neq 0$  then  $a'_0 = 1$ ; thus (A+B-1)will be achieved by eliminating  $a'_0$ . If A = 0 then A+Bwill be computed by removing  $a'_0$ . In this case, we have always  $c_{out} = '0'$  and the sum will be incremented according to equation (7). But incrementing shouldn't be done to obtain the correct result.

The first step of Algorithm 2 reveals that a twostage combinational circuit is required for modulo addition (adder and incrementer). The first stage computes an intermediate sum M.

$$M = A + B - 1$$

if  $A \neq 0$   $(a'_0 = 0)$

$$M = A + B \qquad if A = 0 (a'_0 = 1)$$

Therefore, we adjust equation (7) as below:

$$(A+B) \operatorname{mod} (2^{n}+1) = M + c_{out} + \overline{a'_{0}}$$

(8)

*M* in equation (8) is achieved by addition of *A* and *B* excluding  $a'_0$ . The range of *M* is given by theorem 2.

**Theorem 2** (The range of *M*): *M* has a (n+1)-digit binary representation in CSD-1, i.e.,  $M \in [0, 2^{n+1}]$ . (Note that  $m_n = C_{out}$  in this theorem.)

**Proof:** If A=0 then M=A+B=B. Since  $B \in [0, 2^n]$  then the theorem is established. The situation is the same if B=0.

If  $A \neq 0$  and B? 0 then M = A + B - 1. Since

$$A, B < 2^n + 1, A > 0$$

and  $B > 0$  then,

$0 < A + B - 1 < (2^{n} + 1) + (2^{n} + 1) - 1 \Leftrightarrow 0 < M \le 2^{n+1}$

(9)

The maximal value of M is  $2^{n+1}$  which can be presented by n+2 bits or n+1 digits in CSD-1 (for this maximal value, all bits are '1'). Y

In the second stage, the least n posibits of M is incremented according to (8).

**Step 2:** As described before, if  $A + B \neq 2^n + 1$  then theorem 1 leads to equation (8). But if  $A + B = 2^{n} + 1$ then the correct output of S=0 should be produced. In this case, A and B are non zero and  $M = A + B - 1 = 2^n.$

According to theorem 2 and equation (8), if the msb of  $M, m_n=0$  ( $C_{out} = 0$ ) then M should be incremented in the second stage. Thus the final output is  $2^{n}+1$ . In CSD-1, each number is in the range of  $[0, 2^n]$  and can be represented by n digits. Therefore the output carry can be ignored and the output sum is "0...01" that can be

corrected by inverting  $s_0$ .

In the second step of Algorithm 2, we introduce two methods to detect zero output and to correct it.

- The correct output zero occurs when two inputs are a) complementary, i.e. their sum is equal to modulo  $2^{n}+1$ . One method to recognize complementary numbers is the logical AND of the outputs of  $a_i$ XOR  $b_i$  (for any *i* except i = 0). A similar method has been mentioned in  $[\overline{23}]$ .

- Another method is based on the following theorem. **b**)

Theorem 3: (Complementary of two inputs): Two inputs are complementary when (and only when) the input and output carries of the incrementer are '1'. **Proof:**

First, we prove that if A and B are complementary 0 numbers, the input and output carries of the incrementer are '1'. When A and B are complementary, both of them are non zero. In

Therefore,  $M = A + B - 1 = (2^{n} + 1) - 1 = 2^{n}$ .

CSD-1,  $2^n$  has *n* digits. Thus,  $c_{out} = 0 \Rightarrow \overline{c_{out}} = 1$ . The input carry of the incrementer is  $c_{in}^* = \overline{c_{out}} . a_0' = 1.$

The output carry of the incrementer is equivalent to the output carry of the following addition:

$$S = (A + B - 1) + 1 = A + B = 2^{n} + 1$$

Obviously, the output carry is '1'.

0 Now we prove that if input and output carries of the incrementer are '1' then A and B are complementary numbers.

If  $c_{in}^* = 1$  then  $(\overline{c_{an}} a_0') = 1$ . Therefore  $A \neq 1$ and  $c_{out} = 0$ . In other words, M = A + B - 1 and we have:

$$M = A + B - 1 \le 2^n \Longrightarrow A + B \le 2^n + 1 \tag{10}$$

The output carry of the incrementer is '1' when the sum is equal or more than  $2^{n}+1$ . That is:

$$(A+B-1)+1 \ge 2^n +1 \Longrightarrow A+B \ge 2^n +1$$

(11)

Equations (10) and (11) are simultaneous verified when  $A+B = 2^{n}+1$ , which shows that A and B are complementary.

Y

Method (a) has been used in <sup>[23]</sup>. However the method (b) for zero detection and correction consumes less area than method (a). Then, we implemented method (b). As described earlier and according to example 1,  $s'_0$  can be transformed to '0' in the condition of zero detection.

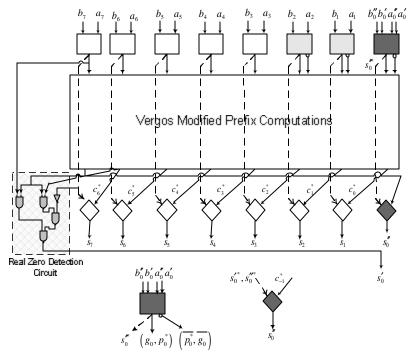

## THE PROPOSEH CSD-1 PARALLEL-PREFIX ADDER (CSD-PP)

One way for implementing the CSD-PP adder is based on the adder architecture of Fig. 2. But instead of having a dedicated single stage for reentering the carry, <sup>[23]</sup> has proposed to perform carry recirculation at each existing prefix level. Then, there is no need for the extra carry increment stage. As a result, a dedicated CSD-PP adder architecture is derived with one less prefix level compared to those derived from Fig. 2 architecture. In the CSD-1 system, it requires several modifications. These modifications will be introduced by the 3 following theorems.

**Theorem 4:** Let assume that  $(\overline{G,P}) = (\overline{G},P)$  and  $G_{a,b}$  and  $P_{a,b}$ , with a > b, are respectively the group generate and propagate signals for the group a, a-1, a-2, ..., *b*-1, *b*, computed by:

$$(G_{a,b}, P_{a,b}) = (g_a, p_a) \circ (g_{a-1}, p_{a-1}) \circ \cdots \circ (g_b, p_b)$$

Y

In our case, in which the reentering carry is given by the expression  $a'_0 \overline{G_{n-1}}$ , the carries  $c^*_i$  of the addition modulo  $2^i+1$  are equal to  $G^*_i$ , where  $G^*_i$  is computed by the prefix equations:

$$\left(G_{i}^{*}, P_{i}^{*}\right) = \begin{cases} \overline{\left(G_{n-1}, P_{n-1}\right)} & i = -1 \\ \left(G_{i}, P_{i}\right) \circ \left(a_{0}^{\prime} \cdot \overline{G_{n-1,i+1}}, P_{n-1,i+1}\right) & if \quad 0 \le i \le n-2 \end{cases}$$

#### **Proof:**

$$\begin{split} & \left(G_{i}^{*}, P_{i}^{*}\right) = \left(G_{i}, P_{i}\right) \circ \left(\overline{G_{n-1}} \cdot a'_{0}, P_{n-1}\right) \\ & = \left(G_{i} + P_{i} \left(\overline{G_{n-1,i+1}} + P_{n-1,i+1} \cdot G_{i}\right) \cdot a'_{0}, P_{n-1}\right) \\ & = \left(G_{i} + P_{i} \overline{G_{n-1,i+1}} \left(\overline{P_{n-1,i+1}} + \overline{G_{i}}\right) \cdot a'_{0}, P_{n-1}\right) \\ & = \left(G_{i} + P_{i} \overline{G_{n-1,i+1}} \overline{P_{n-1,i+1}} \cdot a'_{0} + P_{i} \overline{G_{n-1,i+1}} \overline{G_{i}} \cdot a'_{0}, P_{n-1}\right) \\ & = \left(G_{i} + P_{i} \overline{G_{n-1,i+1}} \cdot a'_{0} + P_{i} \overline{G_{n-1,i+1}} \overline{G_{i}} \cdot a'_{0}, P_{n-1}\right) \\ & = \left(G_{i} + P_{i} \overline{G_{n-1,i+1}} \cdot a'_{0}, P_{i} - 1_{i+1}\right) \\ & = \left(G_{i} + P_{i} \overline{G_{n-1,i+1}} \cdot a'_{0}, P_{n-1,i+1}\right) \\ & = \left(G_{i}, P_{i}\right) \circ \left(\overline{G_{n-1,i+1}} \cdot a'_{0}, P_{n-1,i+1}\right) \end{split}$$

Theorem 5 will derive expressions leading to faster circuits.

**Theorem 5:** Defining

$$p_0^* = p_0 \cdot a'_0$$

leads to

$(G_i^*, P_i^*) = (g_i, p_i) \circ \cdots \circ (g_0, p_0^*) \circ (\overline{G_{n-1,i+1}}, P_{n-1,i+1})$

**Proof:**

$$\begin{pmatrix} G_i^*, P_i^* \end{pmatrix} = (g_i, p_i) \circ \dots \circ (g_0, p_0) \circ (\overline{G_{n-1,i+1}} \cdot a'_0, P_{n-1,i+1}) \\ = \begin{pmatrix} (g_i + p_i g_{i-1} + \dots + p_i p_{i-1} \dots p_1 p_0 \overline{G_{n-1,i+1}} \cdot a'_0) \\ (p_i p_{i-1} \dots p_1 p_0 P_{n-1,i+1}) \end{pmatrix}$$

When computing  $G_i^*$ , only the last term includes  $p_0$  and  $a'_0$ . Therefore, we can define  $p_0^* = p_0 \cdot a'_0$  and replace  $p_0$  by  $p_0^*$

$$\begin{pmatrix} G_{i}^{*}, P_{i}^{*} \end{pmatrix} = (g_{i}, p_{i}) \circ \cdots \circ (g_{0}, p_{0}^{*}) \circ (\overline{G_{n-1,i+1}}, P_{n-1,i+1}) \\ = \begin{pmatrix} (g_{i} + p_{i} g_{i-1} + \cdots + p_{i} p_{i-1} \cdots p_{1} p_{0}^{*} \overline{G_{n-1,i+1}}) \\ , (p_{i} p_{i-1} \cdots p_{1} p_{0}^{*} P_{n-1,i+1}) \end{pmatrix}$$

$$(12)$$

The final  $P_i^*$  are never used and the intermediate  $P_i$  don't have  $p_0$ . The above equations are thus correct. Y

In several cases, the equations (12) require more than  $\log_2 n$  prefix levels for their implementation. These equations can be transformed into equivalent ones that can be implemented within  $\log_2 n$  prefix levels. The required transformation uses Theorem 2 of <sup>[23]</sup>, as well as the Theorem 6 that will be introduced below. Theorem 2 of <sup>[23]</sup> says that,

$$(g, p) \circ \overline{(G, P)} = \overline{(p, g)}, (G, P)$$

This implies that a carry equal to the generate term which is expressed by a prefix equation of the form  $(g, p) \circ \overline{(G, P)}$  is also equal to the generate term of an equation of the form  $\overline{(\overline{p}, \overline{g}), (G, P)}$ .

The above formula is true when  $g \cdot p = p$ .

The following theorem is also required to derive the term that has the form  $(g_0, p_0^*) \circ \overline{(G, P)} = \overline{(\overline{p_0^*}, \overline{g_0})}, (G, P)$  in prefix notation:

**Theorem 6:** If

$$(G_x, P_x) = (g_0, p_0^*) \circ \overline{(G, P)}$$

and

$$(G_y, P_y) = (p_0^*, g_0), (G, P)$$

then  $G_x = G_y$ .

**Proof:** First, we proof the following expression:

$$g_{0} \cdot p_{0}^{*} = (g_{0} + p_{0}^{*}) = a_{0}^{"} b_{0}^{*} + (a_{0}^{"} b_{0}^{*} + b_{0}^{*} a_{0}^{*})$$

$$= \overline{a_{0}^{"} b_{0}^{'} + b_{0}^{"} (a_{0}^{'} + a_{0}^{'})} = \overline{a_{0}^{"} b_{0}^{'} + b_{0}^{'} a_{0}^{'}} = \overline{p_{0}^{*}}$$

(13)

Using this formula, we get:

$$g_{0} + p_{0}^{*}\overline{G} = \overline{(g_{0} + p_{0}^{*}\overline{G})} = \overline{(g_{0} \cdot (p_{0}^{*} + G))}$$

$$= \overline{(g_{0} \cdot p_{0}^{*} + g_{0} \cdot G)} = \overline{(p_{0}^{*} + g_{0} \cdot G)}$$

Y

The carry equations resulting from theorem 2 of  $^{[23]}$  and theorem 6 can be implemented by a prefix structure that has  $\log_2 n$  levels. As mentioned earlier, we use the modifications introduced by theorems 4 to 6. Our proposed adder is similar to  $^{[23]}$  modulo adder architecture but its first cells of preprocessing and post processing stages are designed differently.

In the CSD-1 number system, if  $x'_{0} = 0$  then  $x''_{0} = 0$ . This is a special property of CSD-1. Using this property to simplify truth tables of these two cells leads to the following equations:

$$s_{0}^{"*} = a_{0}^{"} b_{0}^{'} \overline{b_{0}^{"}} + \overline{a_{0}^{"}} b_{0}^{'} b_{0}^{"} = b_{0}^{'} (a_{0}^{"} \oplus b_{0}^{"}),$$

$$p_{0}^{*} = p_{0} \cdot a_{0}^{'} = a_{0}^{"} b_{0}^{'} + a_{0}^{'} b_{0}^{"},$$

$$g_{0} = a_{0}^{"} b_{0}^{"},$$

$$s_{0}^{"} = s_{0}^{"*} \overline{c_{in}^{*}} + s_{0}^{'*} \overline{s_{0}^{"*}} c_{in}^{*},$$

Theorem 3 is used for the detection and generation of a correct zero. The term r indicates the condition of theorem 3:

$$c_{-1} = 1 \rightarrow G_{n-1} \cdot a_0 = 1$$

$$c_{out}^* = 1 \rightarrow h_{n-1} \cdot c_{n-2}^* + g_{n-1} = 1$$

$$r = \overline{c_{-1}^* \cdot c_{out}^*} = \overline{(\overline{G_{n-1}} \cdot a_0')(h_{n-1} \cdot c_{n-2}^* + g_{n-1})}$$

### **RESULTS AND COMPARISONS**

In this section, we compare the proposed CSD-PP adder to those proposed in <sup>[15]</sup> and <sup>[23]</sup>. As previously mentioned, the architecture proposed in <sup>[23]</sup> outperforms those presented in <sup>[24]</sup> and <sup>[25]</sup>, and the architecture proposed in <sup>[15]</sup> outperforms those presented in <sup>[26-28]</sup> in terms of implementation area and execution delay. Thus, the architecture of <sup>[23]</sup> is the best diminished-one architecture, and the architecture of <sup>[15]</sup> is the best architecture using normal binary representation.

All architectures were described in HSPICE and mapped to the 0.18 implementation technology (0.18  $\mu$ m, Vdd=1.8 v). We use VLSI implementations and a simple model to compare the proposed adder architectures to those proposed in <sup>[15]</sup> and <sup>[23]</sup>. We use the notation PPREF for the diminished-one modulo  $2^8$ +1 adder proposed in <sup>[23]</sup> and TPP for the normal binary one in <sup>[15]</sup>. The CSD-PP implementation for the modulo  $2^n$ +1 adder is given in Fig. 2.

Analytical Comparisons and Results: First, we use the analytical model used in <sup>[15]</sup> and <sup>[23]</sup>, under the notation "unit-gate model". This model assumes that each gate, except the exclusive-OR gate, counts as one elementary gate for both area and delay. An exclusive-OR gate counts for two elementary gates for both area and delay. According this model, the latencies of the modulo  $2^n$  and modulo  $2^n$  -1 adders are equal to  $2*\log_2 n$ + 3. The PPREF modulo adder has an execution latency of  $2*\log_2 n + 3$ .

However, according to Fig. 1, the overall delay of PPREF is the modulo adder latency plus the multiplexer delay. The multiplexer is a 2-level circuit in unit-gate model. The overall delay is  $2*\log_2 n + 5$ . The TPP adder has a latency equal to  $2*\log_2 n + 6$  and the proposed CSD-PP adder has a latency equal to  $2*\log_2 n + 4$ . The CSD-PP architecture is faster than PPREF and TPP. Therefore, the CSD-PP adder offers the fastest designs reported in the open literature. The CSD-PP adder has also the same prefix levels as the PPREF adder, without requiring any circuits for treating zero operands as shown in Fig. 1, which reduce both the execution time and the implementation area. Therefore, the proposed CSD-PP adders are more efficient than the fastest modulo  $2^{n}+1$  adder which handle operands in diminished-one representation. The normal binary system can be easily converted to the normal binary RNS. The representation of odd numbers in CSD-PP adders is the same as in TPP adders.

According to the unit-gate model, the hardware overheads of the fastest reported modulo  $2^n$  and modulo  $2^n$  -1 adders are respectively equal to 1.5  $n * \log_2 n + 5n$  and  $3 n * \log_2 n + 5n$ . The PPREF modulo adder has an area of  $4.5 n * \log_2 n + 0.5n + 6$ . However, according to Fig. 1, the final area of PPREF includes the modulo adder area and the area of circuit for the treatment of zero operands. The zero operand circuit area is 2n+5. Thus, the final area is  $4.5 n * \log_2 n + 2.5n + 11$ . The area of the TPP adder is equal to  $4.5 n * \log_2 n + 3.5n + 13$  and the proposed CSD-PP adder area is equal to  $4.5 n * \log_2 n + 0.5n + 15$ .

**Real Comparisons and Results:** For evaluating the speed, area and power consumption efficiencies of each architecture, every adder is implemented by CMOS technology. The obtained results are listed in Table 2. As we can see proposed architecture leads to far faster implementations than that of <sup>[15]</sup> and <sup>[23]</sup>. This is due to the fact that the architecture of <sup>[15]</sup> requires a delay of one CSA unit and the design of PPREF in <sup>[23]</sup> uses some multiplexers to treat zero operands. The proposed architecture, on the other hand, relies on a 2-operand addition (in adverse of TPP that adds two inputs and  $2^n$ -1) and requires unique circuit for zero and non zero operands based on CSD-1 number system.

Fig. 2: Proposed modulo  $2^{n}+1$  parallel-prefix carry save diminished-one adder

| Adder Architecture             | Transistor | Average Power    | Delay (ps) | Power–Delay  |

|--------------------------------|------------|------------------|------------|--------------|

|                                | Count      | Consumption (µW) |            | Product (fJ) |

| PPREF <sup>[23]</sup>          | 1036       | 293.56           | 434.44     | 127.54       |

| TPP <sup>[15]</sup>            | 844        | 278.64           | 562.74     | 156.80       |

| CSD-PP                         | 838        | 214.51           | 235.59     | 50.53        |

| Improvement<br>CSD-PP vs. PREF | > 19%      | < 27%            | > 45%      | > 60%        |

| Improvement<br>CSD-PP vs. TPP  | > 0.7%     | > 23%            | > 58%      | > 67%        |

| Table 2.  | Real | Comparison | Results |

|-----------|------|------------|---------|

| 1 abic 2. | rcai | Comparison | Results |

Finally, we study power consumption of compared architectures. The simulation results are shown in Table 2. It is obvious that the proposed CSD-PP adder has the lowest consumption of all. It improves TPP and PPREF power consumptions above 23% and 26% respectively.

# CONCLUSIONS

In this paper, a new number system has been presented. This paper also presents a new architecture for modulo  $2^n+1$  adders that uses parallel-perfix carry computation units based on mentioned number system. The proposed architecture has better performance than the conventional modulo  $2^{n}+1$  adders. The main points of the paper are summarized below:

- 1. The special treatment required for zero operands in the diminished-one number system has been removed.

- 2. The proposed architecture removes the 3-operand adder issue in the fastest modulo  $2^{n}+1$  adders with the normal binary system.

- 3. The proposed architecture leads to the fastest reported modulo  $2^n+1$  adders, with execution latencies close to the execution latency of the fastest modulo  $2^n$  and modulo  $2^n+1$  adders, which means that the proposed architecture is suitable for RNS applications.

#### REFERENCES

- 1. Behrooz Parhami., 2000. Computer arithmetic: algorithms and hardware designs, Oxford.

- Garner, H., 1959. The residue number system, IRE Trans. On Electronic Computer, vol. EC-8, pp.140-147.

- Kouretas I., and V. Paliouras, 2005. High-radix redundant circuits for RNS modulo r<sup>n</sup>-1, r<sup>n</sup>, or r<sup>n</sup>+ 1, The International Symposium on Circuits and Systems (ISCAS '03), vol. 5.

- Hosseinzade M., S. Timarchi and K. Navi, 2007. Multi Level Residue Number System with Moduli Set of (2<sup>n</sup>, 2<sup>n</sup>-1, 2<sup>n-1</sup>-1), 12<sup>th</sup> International CSI Computer Conference (CSICC'2007).

- Timarchi S., K. Navi and M. Hosseinzade, 2006. New Design of RNS Subtractor for modulo (2<sup>n</sup> +1), 2<sup>nd</sup> IEEE International Conference on Information & Communication Technologies: From Theory To Application.

- Freking W.L. and K.K. Parhi, 1997. Low-power FIR digital filters using residue arithmetic, 31st Asimolar Conference on Signals, Systems and Computers, Pacific Grove, CA, USA, vol. 1, pp. 739–43.

- Fernandez P. G., et al., 2000. A RNS-Based Matrix-Vector-Multiply FCT Architecture for DCT Computation, Proc. of the 43rd IEEE Midwest Symposium on Circuits and Systems, pp. 350-353.

- Parhami B., 1996. A Note on Digital Filter Implementation Using Hybrid RNS-Binary Arithmetic, Signal Processing, vol. 51, pp. 65-67.

- Re A. D., A. Nannareli and M. Re, 2004. A Tools for Arithmetic Generation of RTL-Level VHDL Description of RNS FIR Filters, IEEE Proceeding of the Design, Automation and Test in Europe Conference and Exhibition (DATE).

- Bhardwaj, M. and B. Ljusanin, 1998. The Renaissance – A Residue Number System Based Vector Co-Processor for DSP Dominated Embedded ASICs, Proc. Asimolar Conference on Signals, Systems, and Computers, pp. 202-207.

- Yen S., S. Kim, S. Lim and S. Moon, 2003. RSA Speedup with Chinese Remainder Theorem Immune against Hardware Fault Cryptanalysis, IEEE Trans. On Computers, vol. 52, no. 4, pp. 461-472.

- 12. Hariri A, K. Navi, Rastegarpanah, 2007. A new High Dynamic Range Moduli Set with Efficient Reverse Converter, to appear in Computers & Mathematics with Applications journal (Elsevier).

- Sabbagh A., K. Navi, 2007. An improved Residue to Binary converter for the RNS with Pairs of conjugate moduli, International Conference on Electrical engineering and Informatics.

- Efstathiou C. et al., 2001. On the Design of Modulo 2<sup>n</sup>-1 Adders, Proc. of the Eighth IEEE Int'l Conference on Electronics, Circuits & Systems, pp. 517-520.

- Efstathiou C., H. T. Vergos and D. Nikolos, 2004. Fast Parallel-Prefix 2<sup>n</sup>+1 Adder, IEEE Trans. On Computers, vol. 53, no. 9.

- Taylor F., 1985. A Single Modulus ALU for Signal Processing, IEEE Trans. on Acoustics, Speech, Signal Processing, vol. 33, pp. 1302-1315.

- 17. Leibowitz L. M., 1976. A Simplified Binary Arithmetic for the Fermat Number Transform, IEEE Trans. on Acoustics, Speech, Signal Processing, vol. 24, pp. 356-359.

- Sunder S. at al., 1993. Area-Efficient Diminished-1 Multiplier for Fermat Number-Theoretic Transform, IEE Proc. G, vol. 140, pp. 211-215.

Truong T. K. et al., 1986. Techniques for

- Truong T. K. et al., 1986. Techniques for Computing the Discrete Fourier Transform Using the Quadratic Residue Fermat Number Systems, IEEE Trans. On Computers, vol. 35, pp 1008-1012.

- 20. Zimmermann R. et al., 1994. A 177 Mb/s VLSI Implementation of the International Data Encryption Algorithm, IEEE Journal of Solid-State Circuits, vol. 29, no. 3, pp. 303-307.

- 21. Lehmer D.H., 1951. Proc. of the Second Symposium on Large-Scale Digital Calculating Machinery (Cambridge, MA: Harvard University Press), pp. 141-146.

- 22. Vergos H.T., C. Efstathiou, and D. Nikolos, 2001. High Speed Parallel-Prefix Modulo 2+1 Adders for Diminished-One Operands, IEEE Proce. Of 15th IEEE Symposium on Computer Arithmetic, pp. 211 – 217.

- Vergos H.T., C. Efstathiou, and D. Nikolos, 2002. Diminished-One Modulo 2<sup>n</sup>+1 Adder Design, IEEE Trans. On Computers, vol. 51, pp. 1389-1399.

- 24. Zimmermann R., 1997. Binary Adder Architectures for Cell-Based VLSI and Their Synthesis, PhD thesis, Swiss Federal Institute of Technology.

- 25. Zimmermann R., 1999. Efficient VLSI Implementation of Modulo  $(2^{n}\pm 1)$  Addition and Multiplication, Proc. of the 14th IEEE Symposium on Computer Arithmetic (ARITH-14), Adelaide, Australia, pp. 158-167.

- 26. Bayoumi M. and Jullien G., 1987. A VLSI Implementation of Residue Adders, IEEE Trans. on Circuits and Systems, vol. 34, pp. 284-288.

- Dugdale M., 1992. VLSI Implementation of Residue Adders Based on Binary Adders, IEEE Trans. on Circuits and Systems II, vol. 39, pp. 325-329.

- 28. Hiasat A.A., 2002. High-Speed and Reduced Area Modular Adder Structures for RNS, IEEE Trans. on Computers, pp. 84-89.

- 29. Brent R.P. and H.T. Kung, 1982. A Regular Layout for Parallel Adders, IEEE Trans. on Computers, vol. 31, no. 3, pp. 260-264.

- Kogge P.M. and H.S. Stone, 1973. A Parallel Algorithm for the Efficient Solution of a General Class of Recurrence Equations, IEEE Trans. On Computers, vol. 22, no. 8, pp. 783-791.